Построение таблицы истинности, её анализ и построение таблицы срабатывания сложных систем удобно проводить с использованием ЭВМ.

Для диагностирования логических схем малой и средней степени интеграции успешно применяется логический метод, основанный на активизации путей от входов схемы к ее выходу.

Путь от входа х1 к выходу у схемы будет активизирован в том случае, если при изменении х1 с «О» на «1» или наоборот выходы всех элементов рассматриваемого пути будут изменять свои значения (т. е. элементы срабатывают). Для этого необходимо выбрать определенные значения остальных (активизирующих) входов схемы таким образом, чтобы управляемые элементы, имеющие два (и более) входа, не принадлежащие рассматриваемому пути, не срабатывали. В противном случае будет маскирование срабатывания одних элементов другими, что приведет к ошибке определения достоверности проверки.

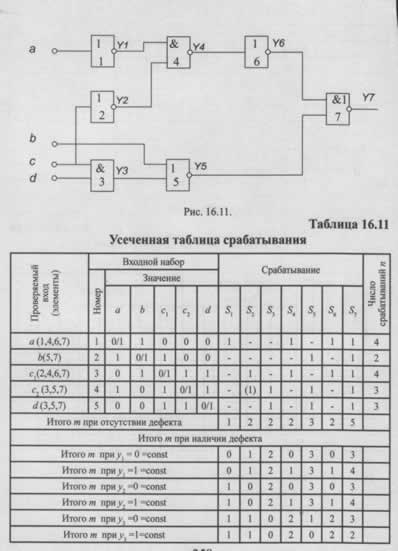

Построим эталонную УТС объекта без использования ЭВМ.

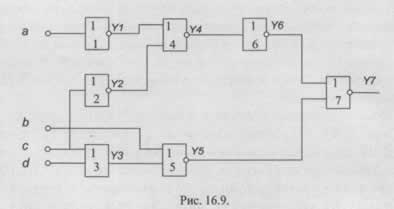

При активизации входа а необходимо, чтобы сработали элементы пути 4, 7, 8, 9. Для срабатывания элемента 4 (элемент ИЛИ) на его второй вход подадим «О», для этом на одном из входов элемента И (d или с) должен быть логический «О». Следующий элемент рассматриваемого пути - элемент 7 (инвертор) будет переключаться, если исправен, при срабатывании элемента 4. Элемент 8 (элемент И) сработает в том случае, если на его втором входе будет логическая «1». Это обеспечивается при d = 0 или Ь = 0. Если принять b = 1, то сработает элемент 6, не принадлежащий рассматриваемому пути. Следовательно, принимаем b = 0. При таком входном наборе сработают все элементы рассматриваемого пути (4, 7, 8, 9). Элементы, не принадлежащие этому пути, в столбце «Срабатывание» отмечены прочерками. Аналогично выбираются входные наборы для проверки остальных путей. При проверке входа Ь2 (элементы 6 и 9) срабатывает элемент 2 (инвертор), который является неуправляемым. Срабатывание этого элемента устранить нельзя. При d = 0 не произойдет срабатывания элементов 5, 8 и 9, не относящихся к рассматриваемому пути. Следовательно, не произойдет маскирования срабатывания элемента 9 по рассматриваемому пути. Аналогично срабатывает элемент 3 при проверке пути d2. При подсчете количества сработавших элементов п срабатывания примыкающих неуправляемых элементов не учитываются. В таблице эти срабатывания отмечены (1). Выбор пути целесообразно проводить таким образом, чтобы в итоге были проверены все входы логических элементов.

В последней строке УТС указано количество срабатываний каждого элемента при подаче на исправную схему всей совокупности входных наборов. Срабатывания примыкающих элементов при подсчете числа т необходимо учитывать. При появлении неисправности количество срабатываний элементов т будет отличаться от их эталонного значения. Для контроля работоспособности объекта достаточно на выходе схемы поставить счетчик, подсчитывающий количество переключений. Поиск неисправного элемента осуществляется ранее описанным методом.

Можно установить некоторые закономерности прохождения сигнала от х1 до у. Активизируемый сигнал х проходит через элементы И, И-НЕ, если на все активизирующие его входы подать логическую «1». Активизируемый сигнал х проходит через элементы ИЛИ, ИЛИ-НЕ, если на все активизирующие его входы подать логический «О». Учитывая эти закономерности логических элементов, можно диагностировать ИМС малой и средней степени интеграции в судовых условиях с помощью простейших малогабаритных приборов тестового диагностирования. В качестве формирователя тестовых наборов можно использовать автоматическое бесконтактное переключающее устройство (АБПУ), дополнив его диодной матрицей или электрически программируемым ПЗУ. Записи уравнений переключательных функций в этом случае не требуется.

Рассмотренные методы контроля и поиска неисправного логического элемента позволяют значительно сократить время пребывания объекта в неработоспособном состоянии и уменьшить количество возможных отказов оборудования.

При оценке эффективности методов контроля целесообразно использовать следующие частные показатели: время построения проверяющего теста и теста поиска дефектов, время определения работоспособности объекта контроля и локализации отказавших элементов, средняя глубина поиска дефектов, количество контрольных точек, достоверность контроля и локализации отказавшего элемента, масса, габариты и стоимость средств контроля.

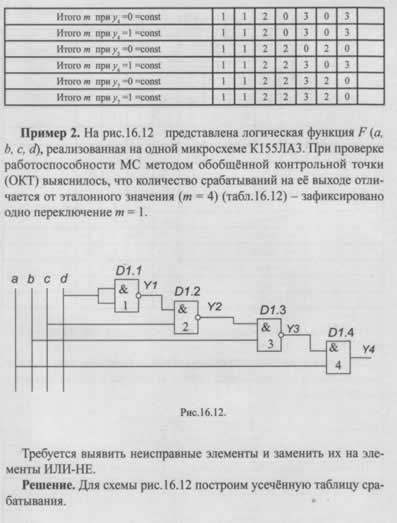

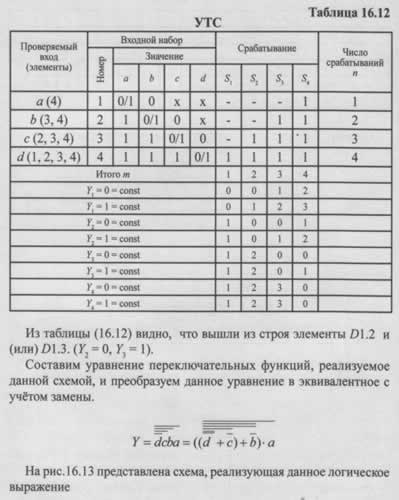

Пример схемы, требующей изменение структуры на время диагностирования.

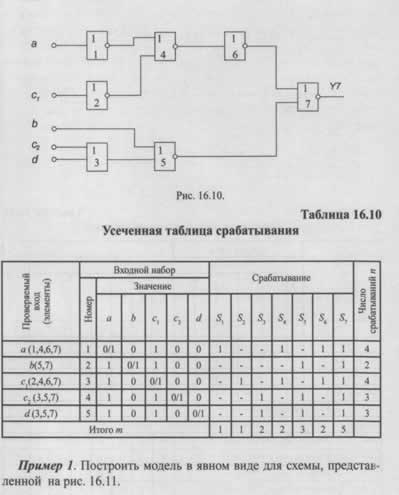

Данная схема требует распайки входа с, так как при активизации входа b и прохождения импульсов через элемент 7 необходимо обеспечить Y6 = 0. Для этого необходимо выполнить условие с =1. Это противоречит условию прохождения сигнала b = 0/1, так как на выходе элемента 5 всегда будет единица (У5 =1). Кроме того, при активизации входов с2 и d и срабатывании элемента 5 элемент 6 (У6) также будет срабатывать. Следовательно, произойдёт маскирование срабатываний одного элемента другим (элементы 5 и 6). Схема с распайкой входа с представлена на рисунке 16.10.

Усеченная таблица срабатывания для схемы с учётом распайки входа с представлена в табл. 16.10. Следует заметить, что изменение структуры схемы отражено в графе входных наборов УТС (вход с разбит на два входа: с1 и с2).