Арифметическое устройство — одно из главных устройств цифровой электронной вычислительной машины, в котором выполняются логические и арифметические операции над числами.

Осуществление любой логической или арифметической операции в арифметическом устройстве сводится, в конечном счете, к последовательному выполнению нескольких микроопераций или элементарных операций: установка в «ноль» любых разрядов блоков арифметического устройства, прием отдельного разряда или кода числа, сдвиг в сторону старших или младших разрядов числа, получение инверсного (обратного) кода, сложение кодов, выдача кода и т. д.

К арифметическим операциям можно отнести сложение, извлечение корня, умножение, деление и вычитание. Деление и извлечение корня, а также возведение числа в степень, определение тригонометрических функций, логарифмов и т. п. весьма часто осуществляются по стандартным подпрограммам. Главная операция цифровой вычислительной машины — сложение, к которому сводятся все другие арифметические операции. Например, умножение сводится к суммированию несколько раз множимого; деление — к поочередному нахождению цифр частного при помощи вычитания и сложения.

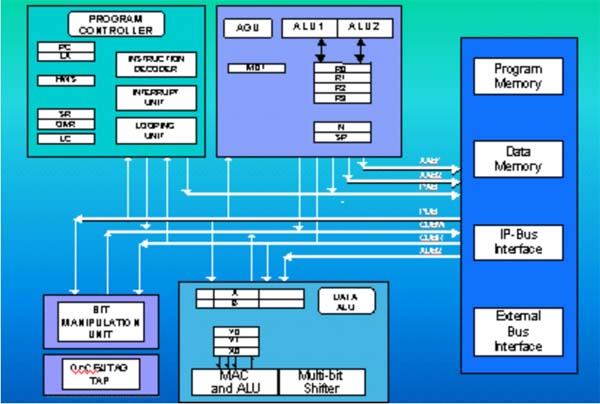

Арифметическое устройство в составе цифровой вычислительной машины связано с центральным устройством управления. Из запоминающего устройства поступают первоначальные числа, по команде центрального устройства управления («умножить», «вычесть», «сложить» и т. д.). Арифметическое устройство производит соответствующие операции, после чего результаты операций снова передаются в запоминающее устройство, а сигналы, означающие окончание операции, показатели переполнения разрядной сетки и т. п., при необходимости передаются в центральное устройство управления.

Главные характеристики и состав арифметического устройства зависят от требуемого быстродействия, разрядности чисел, выбранной системы счисления, алгоритмов выполнения операций и их ускорения, типа применяемых схем и связей между ними (импульсно-потенциальные, импульсные или потенциальные) и формы представления чисел.

Арифметическое устройство, как правило, состоит из нескольких регистров для недолговременного хранения чисел, логических цепей, предназначенных для выполнения простейших операций над числами, сумматоров и местного устройства управления, которое воспринимает команду на произведение операции от центрального устройства управления машины и отрабатывающего нужную последовательность команд.

В зависимости от используемого способа суммирования чисел различают арифметические устройства последовательно-параллельного, параллельного и последовательного действия. В арифметических устройствах последовательного действия суммирование двух чисел осуществляется одноразрядным сумматором, через который поэтапно, начиная с младших, проходят все имеющиеся разряды слагаемых. В арифметических устройствах параллельного действия все разряды каждого из слагаемых подаются в сумматор одновременно, количество разрядов сумматора равно количеству разрядов в слагаемых.

Арифметические устройства последовательно-параллельного действия являются промежуточной формой. Регистры параллельного арифметического устройства состоят из триггеров или подобных элементов и позволяют произвести одновременный доступ ко всем разрядам числа. В арифметическом устройстве последовательного действия вместо регистров применяются в том числе и линии задержки, которые, в случае необходимости, замыкаются в кольцо через логические цепи рециркуляции и усилители. В элементах и схемах арифметического устройства применяются электронные лампы (в первоначальных образцах), полупроводниковые диоды, транзисторы, феррит-диодные ячейки и феррит-транзисторные ячейки.

В арифметических устройствах с микропрограммным управлением в составе местного устройства управления используют также ферритовые матрицы, предназначенные для хранения микропрограмм операций.

Основные требования к элементам схем арифметического устройства — высокая надежность, технологичность, взаимозаменяемость однотипных элементов, повторяемость главных характеристик в производстве.

С учетом способа кодирования чисел арифметические устройства производятся для операций в десятичной или двоичной системе, реже — в троичной, либо какой-нибудь иной системе счисления, с разным количеством разрядов, с числами, представленными в форме с плавающей или с фиксированной запятой, или и с теми и с другими.

Методы ускорения выполнения операций используются либо в элементарных операциях, либо в полных операциях арифметического устройства. Особенно результативно ускорение элементарной операции суммирования, потому что она большей частью входит в алгебраическое сложение или вычитание, деление, умножение и др.

В последовательных арифметических устройствах ускорение суммирования получается переходом к последовательно-параллельным схемам; соответственно в параллельных — использованием схем, применяющих статистический характер переносов, схем «с мгновенным переносом» и т. п. Наиболее изучены методы ускорения умножения. В последовательных приспособлениях они базируются главным образом на введении дополнительных сумматоров, которые позволяют одновременно суммировать несколько частичных произведений; в пределе наличие п сумматоров последовательного типа (или п/2 логических схем и сумматоров) позволяет произвести умножение за 2п тактов. В параллельных арифметических устройствах используются методы ускорения умножения аппаратные и логические 1-го и 2-го порядка. Логические методы базируются на модификации множителя; увеличение количества аппаратуры при их применении касается только местного устройства управления и не зависит от числа разрядов в перемножаемых числах; практический и теоретический предел возможностей логических методов — уменьшение среднего числа суммирований при осуществлении одного умножения до 1/3 на каждый двоичный разряд множителя. Аппаратные методы 1-го порядка базируются на введении вспомогательных сумматоров, вспомогательных цепей запоминания переносов или замещении цепей сдвига цепями деления и умножения на особые множители; количество вспомогательного оборудования пропорционально количеству разрядов; число тактов суммирования в процессе умножения трансцендентно может быть уменьшено до одного (независимо от числа разрядов множителя), однако в действительности этот предел не достижим. Аппаратные методы 2-го порядка базируются на построении пирамид сумматоров; объем оборудования пропорционален квадрату количества разрядов, время умножения равносильно 2—3 тактам суммирования. Подобные методы разрабатываются для ускорения операции деления.

Главные тенденции в развитии арифметических устройств связаны с использованием микроэлектроники. Вследствие чего применяются матричные схемы для прямого суммирования и умножения десятичных цифр, параллель-но-параллельные и сверхпараллельные сумматоры, аппаратные методы 2-го порядка для ускорения деления и умножения, другими словами, построения с большим числом повторяющихся элементов и систематическими связями между ними. Ищутся также новые способы кодирования чисел, которые упрощают выполнение операций, иные методы ускорения операций, исправления ошибок и аппаратного контроля. При этом ставятся цели повышения быстродействия, увеличения надежности, уменьшения стоимости потребляемой мощности и габаритов.