Анализ таблиц истинности, а также построение и проверка таблиц срабатывания для сложных цифровых систем значительно упрощаются при использовании вычислительной техники. Однако существует эффективный ручной подход для схем малой и средней степени интеграции.

Суть логического метода диагностики

В основе метода лежит принцип активизации путей от входов схемы к её выходу. Путь считается активизированным, если изменение логического уровня на стартовом входе (например, с 0 на 1) вызывает последовательное переключение всех элементов на этом пути. Для этого необходимо тщательно подобрать значения на других (активизирующих) входах схемы. Ключевая задача — обеспечить, чтобы элементы с несколькими входами, не входящие в проверяемый путь, оставались в стабильном состоянии и не маскировали срабатывание целевой цепочки.

Построение эталонной УТС: практический пример

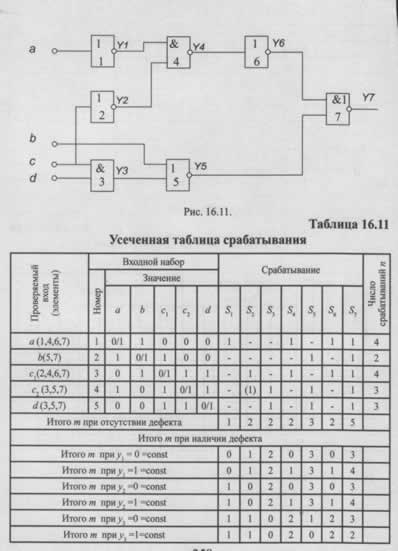

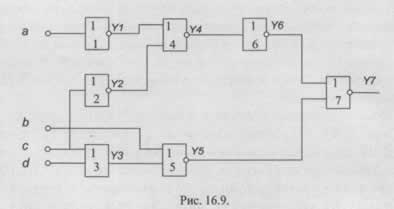

Рассмотрим процесс построения эталонной Универсальной Таблицы Срабатывания (УТС) без использования ЭВМ на конкретном примере. Для активизации пути от входа a через элементы 4, 7, 8, 9 необходимо:

- Для срабатывания элемента ИЛИ (4) на его второй вход подается «0». Это требует, чтобы на одном из входов предшествующего элемента И был логический «0» (на входе d или c).

- Инвертор (7) сработает автоматически при переключении элемента 4.

- Элемент И (8) активируется, если на его втором входе будет «1». Это условие выполняется при d=0 или b=0. Однако если выбрать b=1, сработает посторонний элемент 6, что недопустимо. Следовательно, выбирается b=0.

При таком входном наборе сработает весь целевой путь. Элементы, не входящие в путь, в столбце «Срабатывание» отмечаются прочерком. Аналогичным образом подбираются наборы для проверки всех остальных путей в схеме.

Особые случаи и учет срабатываний

В процессе диагностики встречаются особые ситуации. Например, при проверке пути для входа b2 (элементы 6, 9) неизбежно срабатывает инвертор (2), который является неуправляемым в данном контексте. Его срабатывание исключить нельзя, но оно не должно мешать проверке основного пути. Для этого, например, устанавливается d=0, что блокирует срабатывание посторонних элементов 5, 8, 9 и предотвращает маскировку.

Важно различать два типа подсчета:

- При построении УТС (n): срабатывания примыкающих неуправляемых элементов (помеченные как (1)) не учитываются в количестве срабатываний для проверки пути.

- В эталонной строке УТС (m): подсчитывается общее количество срабатываний каждого элемента при подаче всех тестовых наборов на исправную схему. Здесь учитываются все срабатывания, включая примыкающие. Отклонение от этих эталонных значений m при тестировании указывает на наличие неисправности.

Закономерности и практическое применение

Можно сформулировать общие правила прохождения активизирующего сигнала:

- Через элементы И, И-НЕ сигнал проходит, если на все их управляющие входы подана логическая «1».

- Через элементы ИЛИ, ИЛИ-НЕ сигнал проходит, если на все их управляющие входы подана логическая «0».

Использование этих закономерностей позволяет диагностировать интегральные микросхемы в полевых условиях (например, на судах) с помощью простых портативных тестеров. В качестве формирователя тестовых наборов может выступать автоматическое бесконтактное переключающее устройство (АБПУ), дополненное диодной матрицей или ПЗУ, что избавляет от необходимости составления сложных переключательных функций.

Эффективность и модификация схем

Применение логических методов контроля и поиска неисправностей существенно сокращает время простоя оборудования и снижает риск последующих отказов. Для оценки эффективности методов используются такие показатели, как время построения тестов, скорость локализации неисправности, глубина поиска, достоверность, а также масса, габариты и стоимость контрольного оборудования.

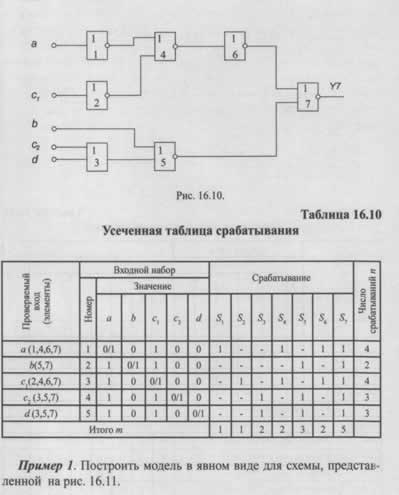

Иногда для успешной диагностики требуется временная модификация структуры схемы. Например, в приведенной схеме для активизации пути через вход b и элемент 7 необходимо обеспечить Y6 = 0, что требует условия c = 1. Однако это противоречит условию прохождения сигнала b и приводит к постоянной «1» на выходе элемента 5 (У5 =1), что вызывает маскирование срабатываний элементов 5 и 6. Решением является временная распайка входа c на два независимых входа: c1 и c2. Эта модификация отражается в графе входных наборов УТС.

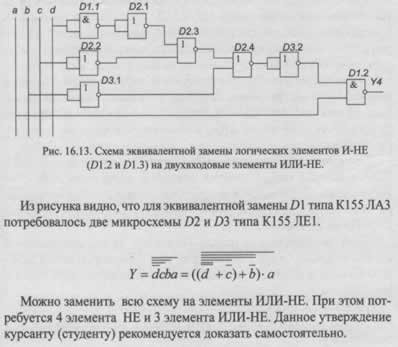

Схема с распайкой входа с представлена на рисунке 16.10.