Метод обобщенной контрольной точки — это эффективный подход к диагностике логических схем, который позволяет значительно снизить затраты на разработку и обслуживание систем контроля. Его основная идея заключается в использовании минимального набора информативных параметров, измеряемых в одной контрольной точке, например, на шине питания или выходных контактах устройства. Часто в качестве такого обобщенного параметра выбирается ток потребления схемы. В отличие от традиционных методов, фиксирующих статические состояния («0» или «1»), данный метод регистрирует динамический факт — переход системы из одного состояния в другое при изменении входного сигнала объекта диагностики (ОД).

Условия обнаружения неисправностей

Ключевым условием для успешного обнаружения неисправности этим методом является отсутствие маскирования, когда срабатывание одного элемента скрывает срабатывание другого. Для этого необходимо обеспечить последовательное во времени срабатывание элементов с достаточным интервалом между ними, позволяющим их четко разделить. Первичная задача — построение тестов, которые разбивают ОД на одномерные пути (цепочки логически связанных элементов). Если достоверность проверки с помощью таких тестов окажется недостаточной, требуется применение дополнительных технических методов для дальнейшего разделения сигналов.

Оптимальный алгоритм диагностирования

Процесс технического диагностирования логических схем по этому методу включает несколько последовательных этапов:

- Построение функциональной схемы ОД. Глубина детализации схемы определяется требуемым уровнем диагностики.

- Разработка математической модели. На основе функциональной схемы создается формальная модель, сложность которой зависит от необходимой достоверности диагностики.

- Построение тестов. Создаются проверяющие тесты (ПТ) для определения наличия неисправности и тесты поиска дефектов (ТПД) для их локализации.

- Оптимизация тестов. Проводится минимизация построенных ПТ и ТПД для повышения эффективности.

Детализация этапов

Построение функциональной схемы выполняется в строгой последовательности: выбор необходимых логических элементов по условным обозначениям, их соединение в соответствии с направлением сигналов и компоновка по рангам (входы ОД считаются нулевым рангом).

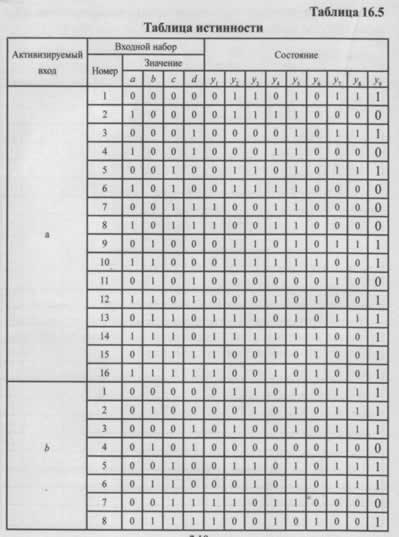

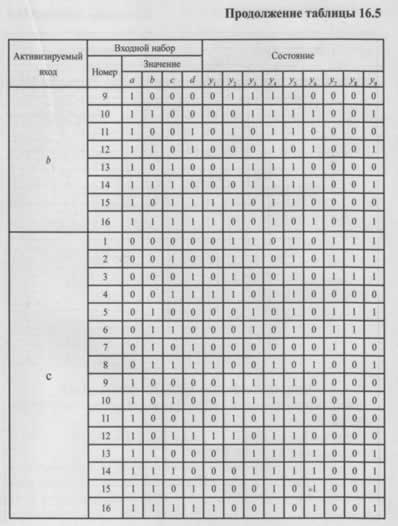

Математическая модель представляет собой формальное описание работы ОД в исправном и всех возможных неисправных состояниях. Для логических схем наиболее наглядной моделью является таблица истинности, где для каждого входного набора фиксируется состояние каждого элемента схемы.

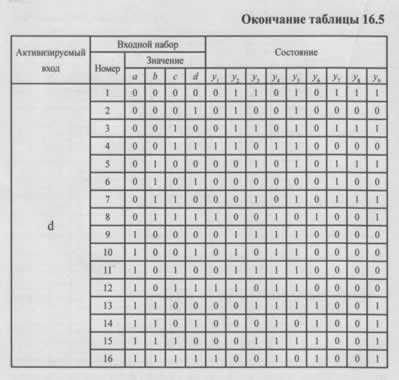

Поскольку метод основан на регистрации переходов, удобнее работать не с таблицей истинности, а с таблицей срабатывания, которая фиксирует моменты изменения состояния элементов. Именно эти таблицы используются для синтеза минимальных по длине тестов.

Практический пример и построение таблиц

Рассмотрим методику построения минимальных проверяющих тестов на примере комбинационной логической схемы.

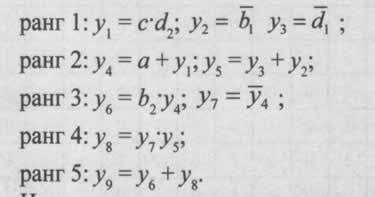

Для формального описания схемы используется система уравнений непосредственных связей, где переменные обозначают входы схемы и выходы ее логических элементов. Для каждого ранга элементов записывается своя система уравнений.

На основе этих уравнений для каждого элемента определяются выходные значения при всех возможных входных наборах, что позволяет заполнить таблицу истинности.

Порядок построения таблицы срабатываний

Важно отметить, что для одного и того же входа может существовать несколько одномерных путей распространения сигнала. В случае разветвления цепей на входах (например, вход b и d на рис. 16.7) их рассматривают как отдельные входы (рис. 16.8). Элементы, не входящие в анализируемый одномерный путь, считаются пассивными, и в соответствующих клетках таблицы срабатывания ставится прочерк «-».

В таблицу заносятся результаты вычислений для каждой пары входных наборов, вызывающих срабатывание элементов активного пути. Единицы в строке суммируются, и результат записывается в графу «число срабатываний» (единицы в скобках при этом не учитываются).

По функциональной схеме определяются все одномерные пути и перечисляются входящие в них элементы. Если для входа существует несколько путей, предпочтение отдается наиболее длинному, так как он охватывает проверкой максимальное количество элементов схемы, повышая полноту диагностики.