Сущность метода обобщенной контрольной точки заключается в выборе минимального количества (как правило, одного) информативных параметров в одной контрольной точке (шины питания и выходные контакты объекта контроля). В качестве обобщенного параметра может рассматриваться ток питания схемы. Этот метод позволяет сократить стоимость разработки и обслуживания средств контроля. Он предполагает не определение «О» или «1», а регистрацию факта перехода системы из одного состояния в другое при изменении параметра сигнала на входе ОД.

Условием обнаружения неисправности в объекте методом обобщенной контрольной точки является отсутствие маскирования срабатывания одного элемента другим, т. е. любой ОД необходимо контролировать таким образом, чтобы элементы срабатывали во времени последовательно и моменты срабатывания отстояли друг от друга на расстоянии, позволяющем производить их разделение. Для такого разделения необходимо производить, в первую очередь, построение тестов, разбивающих ОД на одномерные пути. Если достоверность проверки объекта с помощью таких тестов не равна единице, необходимо применять технические методы дальнейшего разделения ОД.

Оптимальный алгоритм технического диагностирования логических схем включает следующие этапы:

- построение функциональной схемы ОД, при этом состав элементов определяется требуемой глубиной диагностирования;

- построение по функциональной схеме математической модели, степень сложности которой определяется требуемой достоверностью результатов технического диагностирования;

- построение проверяющих тестов (ПТ) и тестов поиска дефектов (ТПД);

- оптимизацию (минимизацию) ПТ и ТПД.

Построение функциональной схемы ОД осуществляется в такой последовательности:

а) используя условные обозначения элементов, определяются те, которые необходимы для построения схемы;

б) элементы соединяются линиями со стрелками, при этом направления стрелок соответствуют направлениям передачи сигналов;

в) в «строках» располагаются входы ОД, в «столбцах» - элементы по рангам (см. рис. 16.7). В качестве нулевого ранга используются входы ОД.

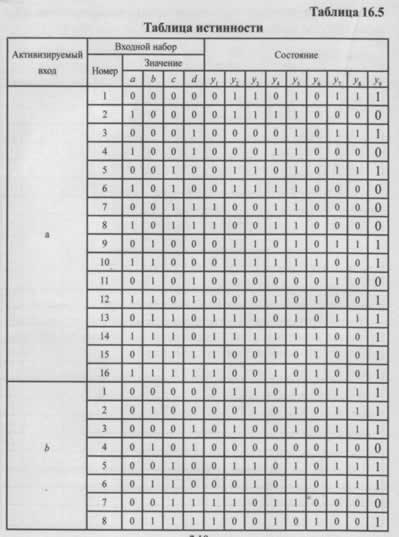

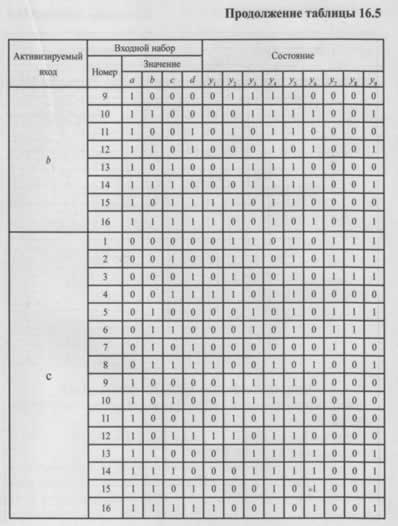

Под математической моделью ОД понимается формальное описание его поведения в исправном и неисправном состоянии. Наиболее удобной моделью логических схем является таблица истинности. В клетку таблицы истинности, находящуюся на пересечении i-й строки и j-го столбца, записывается результат воздействия i-гo входного набора на j-й элемент.

Так как метод обобщенной контрольной точки основан на регистрации факта перехода элементов схемы из одного состояния в другое, для реализации этого метода удобнее перейти от таблицы истинности к таблице срабатывания объекта. Построенные таблицы срабатываний используются для нахождения минимальных тестов.

Рассмотрим методику построения минимальных проверяющих тестов (ПТ) для комбинационной логической схемы (рис. 16.7).

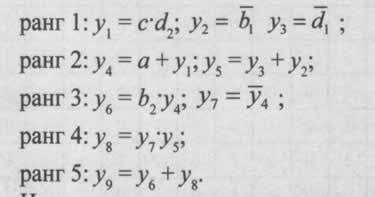

Для описания логической схемы можно использовать систему уравнений непосредственных связей. С этой целью в уравнения вводятся обозначения переменных, соответствующие входам схемы и выходам логических элементов схемы. Для каждого ранга записывается система уравнений, описывающая работу элементов:

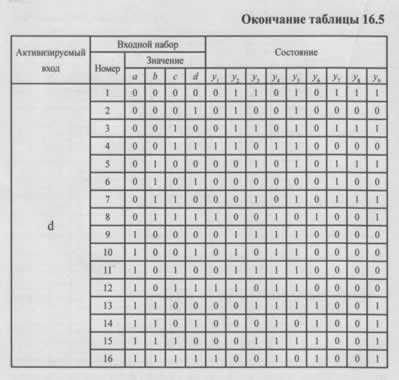

Используя эти уравнения, для каждого элемента определяют значения выходных функций на всех входах схемы и заполняют таблицу истинности, аналогичную табл. 16.5.

Порядок построения таблицы срабатываний

При проверке одного и того же входа может существовать несколько одномерных путей.

При разветвлении цепей на входах схемы bad (рис. 16.7) их выделяют в отдельные входы (рис. 16.8).

Элементы, не относящиеся к одномерному пути, считаются пассивными, и в клетках таблицы срабатывания, соответствующих этим элементам, проставляются прочерки «-»(например, путь а, элементы 1,2,3,5,6).

Здесь i=1,..., n - номер элемента в схеме; k= 1,3,5,... (2m - 1) (где m - число входов проверяемого объекта).

Результаты вычислений заносятся в соответствующие клетки таблицы (нули не проставляются). Единицы в строке соответствующей пары наборов складываются, и в клетке «число срабатываний» записывается результат сложения. При этом единицы, заключенные в скобках (1), не учитываются.

По функциональной схеме (см. рис. 16.8) определяют одномерные пути и выписывают элементы, входящие в них. Для одних входов может быть только один одномерный путь (вход а или с), другие входы могут содержать несколько таких путей (входы b и d). При выборе одного из них предпочтение отдается наиболее длинному пути, так как при этом охватывается наибольшее количество проверяемых элементов.